全球人工智慧(AI)算力需求如海嘯般快速席捲,傳統晶片設計遭受挑戰。驅動IC龍頭聯詠以破釜沉舟之姿,插旗高難度、高門檻的資料中心AI ASIC;聯詠透露,已投入逾2億美元發展包括晶片設計在內的AI伺服器生態系統,與台積電、Arm(安謀)等生態巨擘緊密結盟,多款應用產品定調3、5奈米製程打造,縮短晶片開發周期,以應對AI每天高達10的20次方的巨量運算需求。

目前AI應用的Query(請求)數目每日高達50億次,且未來由多重應用整合的「Agentic AI」將導致算力需求呈現十倍、百倍的爆炸性增長。聯詠協理平德林分析,目前限制AI發展的唯一因素,不再是投資規模,而是電力設施的強度;追求極致的功耗效率(Power Efficiency),將成決勝關鍵。

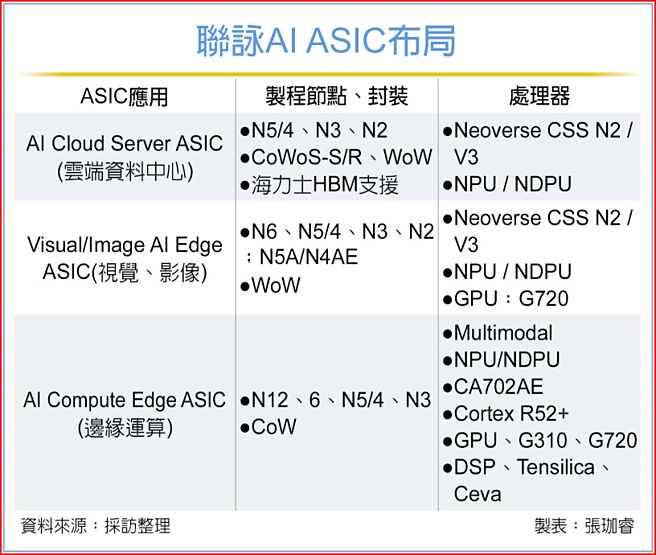

衝刺AI時代發展,聯詠與Arm、台積電合作緊密,投注資源發展ASIC。平德林透露,單一3奈米AI資料中心ASIC之投資規模已達百億新台幣,而下一代2奈米專案更將落在2億美元。面對龐大投資,聯詠認為,唯一回收方法,就是讓ASIC的算力效能必須高於一般GPU算力。

聯詠以台積電N4P打造之AI資料中心ASIC,為基於Arm CSS N2架構,為複雜度極高的異質整合;同時該晶片採用先進的CoWoS封裝、尺寸達77.5x77.5mm2(平方毫米);內部架構高度整合,包含16個CPU核心、結合四個專屬加速器及HBM3E記憶體。

在晶片設計上,聯詠展示其技術實力已達到業界的頂級水準。平德林指出,面對先進製程漫長的時間及高昂的除錯成本,聯詠翻轉設計觀念,從傳統的「湊起來」(Bottom-Up)轉變為「由上而下」(Top-Down)來設計晶片。

聯詠更打造軟體模擬平台進行完整硬體軟體共同驗證。助攻聯詠在晶片Tape-out(流片)前,就將所有生態系統的效能、功耗等參數進行收斂,甚至將Loop Cycle壓縮至每日一次,從根本上避免收到樣片後,才發現問題導致需要額外耗費八個月進行二次流片。

發表意見

中時新聞網對留言系統使用者發布的文字、圖片或檔案保有片面修改或移除的權利。當使用者使用本網站留言服務時,表示已詳細閱讀並完全了解,且同意配合下述規定:

違反上述規定者,中時新聞網有權刪除留言,或者直接封鎖帳號!請使用者在發言前,務必先閱讀留言板規則,謝謝配合。