搜尋結果

以下是含有Xilinx的搜尋結果,共17筆

-

台積洩密案掀波 專家籲立敏感科技法

晶圓代工龍頭台積電11日將舉行董事會,會中將討論第2季股利、資本支出計畫,預期將報告營業祕密外洩的相關案情,2名副總級主管被拍到搭乘高鐵前往台南;另有業內人士質疑,營業祕密外洩事件從外洩方式到對象都不合理,不排除是國家勢力在背後推動。專家則呼籲政府應評估創設《敏感科技保護法》。

-

不只超微狂吞市場!3台廠瘋併購 搶攻下一波成長關鍵武器

市場變化加劇,靠併購加速跨域整合,已成為搶占下一波成長曲線的關鍵武器;不少台廠近年亦透過收購切入新市場、補強產品線,加快擴張版圖。

-

擷發科技前進Embedded World 2025 推出客製化ASIC服務

在嵌入式科技界年度盛事Embedded World 2025上,台灣半導體黑馬擷發科技(7796)以「AI軟硬整合雙引擎」橫掃國際舞台,透過革命性CAPS跨平台AI方案與CATS客製化ASIC服務,短短三日締結破百項合作商機,較去年成長超過300%。其中,ASIC服務於歐美市場引發熱烈迴響。

-

《興櫃股》擷發科技亮相Embedded World 成功締結百筆商機

擷發科(7796)於德國紐倫堡舉行的全球嵌入式技術年度盛會Embedded World 2025 (EW2025)上,以CAPS(Cross-Platform AI Powered Solutions)「跨平台AI軟體服務」及CATS(Custom ASIC Technology and Solutions)「客製化ASIC設計服務」驚艷全球市場,吸引眾多企業洽談合作。展會期間,擷發科技成功締結超過百筆潛在商機,較去年成長超過三倍,展現跨平台AI軟體服務與ASIC設計服務的市場需求。

-

擷發科 攻邊緣運算軟硬整合

專注於「ASIC設計服務」與「AI軟體設計平台」之擷發科技,憑藉軟硬整合技術實力,營收進入高成長,累計今年前2個月合併營收年增達219%。隨AI技術普及與市場對高效能、低成本解決方案的需求增加,擷發AI軟體設計平台展現強大的市場競爭力。董事長楊健盟分析,DeepSeek或Manus等小模型、代理AI模型興起,邊緣運算軟硬整合,將較GPU更有競爭力。

-

俄羅斯S-70「獵人」飛翼無人機 有寫著TAIWAN的西方晶片

烏克蘭國防情報局(GUR)聲稱,在上個月,被擊落的俄羅斯S-70「獵人B」 (Okhotnik-B)飛翼式無人機已完成調查,發現它安裝了數十個西方製造的零件。在GUR公布的照片中,一枚賽靈思-AMD(Xilinx-AMD)晶片是台灣代工的,因為上面就寫著TAIWAN。

-

《電週邊》宜鼎前9月營收增8% 推安全裝備AI辨識解決方案

宜鼎(5289)今年9月營收7.12億元,年增2.35%、月減9.71%;前9月營收66.87億元,年增8.15%。宜鼎運用AI協助改善工作場所安全性,推出全方位涵蓋軟硬體及警示系統的「InnoPPE安全裝備辨識解決方案」;一台InnoPPE邊緣AI主機即可同時辨識來自4路以上攝影機的即時影像,準確偵測進廠人員是否依規範穿著反光背心、護目鏡等安全裝備。InnoPPE由AI模型、軟體操作介面到硬體架構皆可客製開發,其中宜鼎更可根據客戶環境、特定裝備項目等變因,提供自主研發的專屬AI辨識模型,並依場域需求置換辨識項目,確保高度彈性。

-

英特爾求生 賣業務、停建德廠

為度過英特爾逾半世紀以來最大營運危機,路透引述知情人士指出,執行長基辛格(Pat Gelsinger)與其他高層將在本月中旬向董事會提出整頓計畫,當中包括叫停德國建廠計畫與可能出售可程式化邏輯閘陣列(FPGA)大廠Altera等,但將晶圓代工業務售出給台積電等買主,則並沒有納入提案中。

-

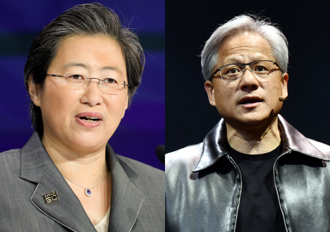

2大晶片CEO同是一家人 黃仁勳透露眼中的蘇姿丰

輝達(NVIDIA)創辦人黃仁勳、超微(AMD)執行長蘇姿丰一樣出生於台南,兩人是遠房親戚的關係,蘇姿丰的外公與黃仁勳的媽媽是兄妹,根據財經新聞網站《Benzinga》報導,黃仁勳過去在媒體採訪中,提到蘇姿丰時稱她為家人而不是競爭對手,並稱讚她非常了不起。

-

超微 AI加持 淨利年增近9倍

AI晶片二哥超微(AMD)30日公布第二季業績,AI晶片需求刺激上季淨利年增近9倍,且資料中心營收激增逾一倍,加上本季財測優於市場預期,帶動超微股價大漲。

-

輝達狂瀉7% 救台積電時代過去?陸行之曝新救世主變它

美國晶片股大暴跌,輝達股價重挫7.04%,台積電ADR跌幅也高達3.4%,半導體分析師陸行之在臉書撰文指出,AMD(超微)第2季財報與第3季財測雙優於預期,盤後股價上漲超過7%,他去年曾經說過一個輝達救台積電,這次看看會不會輪到AMD救台積電一次。

-

輝達狂瀉7% 救台積電時代過去?陸行之曝新救世主變它

美國晶片股大暴跌,輝達股價重挫7.04%,台積電ADR跌幅也高達3.4%,半導體分析師陸行之在臉書撰文指出,AMD(超微)第2季財報與第3季財測雙優於預期,盤後股價上漲超過7%,他去年曾經說過一個輝達救台積電,這次看看會不會輪到AMD救台積電一次。

-

輝達首贏高通 稱霸IC設計

2023年全球前十大IC設計業者大洗牌,TrendForce調查,輝達(NIVIDA)首次超越高通,穩坐IC設計寶座,前十大業者營收合計約1,677億美元,年增12%。

-

全球10大IC設計廠營收 輝達首度奪冠大增105%

去年半導體產業不景氣,不過調研機構TrendForce統計,2023年全球前10大IC設計公司營收合計約1,676億美元,年增12%,其中引領AI浪潮的輝達,營收更成長105%。

-

AI晶片獨木難撐…超微 本季財測不如預期

超微(AMD)上季(1至3月)受惠於AI需求,營收54.7億美元優於華爾街預期,且與去年同期相比轉虧為盈,但本季財測和市場展望不如預期,使公司股價1日早盤下跌7.99%。

-

AI重磅又一波!AMD蘇姿丰領軍劍指大陸市場

重磅AI一波波!繼輝達的「GTC 2024」後,AMD「AI PC創新峰會」登場,大秀大陸市場AI PC產業體系的動能,除AMD董事長暨執行長蘇姿丰外,合作夥伴一字排開力挺,AMD董事長暨執行長蘇姿丰表示,AI正在掀起一場革命,AMD Ryzen AI將實現從雲端到PC的無縫AI體驗。另外,AMD也正式將Ryzen 8040系列以及Ryzen 8000G桌上型解決方案推向大陸市場。

-

蘇姿丰 帶超微浴火重生的半導體女王

AI的橫空出世,是2023年全球科技產業最熱門的話題,而引領這股風潮的三位風雲人物─黃仁勳、蘇姿丰與梁見後,均擁有台灣背景,他們在國際舞台上各領風騷,成為台灣科技實力在全球領域裡發光發熱的象徵。